# **OmpSs-2@FPGA User Guide**

Release 3.1.1

**BSC Programming Models**

# **CONTENTS**

| 1 | Insta | all OmpSs-2@FPGA toolchain                                            | 3  |  |  |

|---|-------|-----------------------------------------------------------------------|----|--|--|

|   | 1.1   | Prerequisites                                                         | 3  |  |  |

|   |       | 1.1.1 Git Large File Storage                                          | 3  |  |  |

|   |       | 1.1.2 Vendor backends - Xilinx Vivado                                 | 3  |  |  |

|   | 1.2   | Stable release                                                        | 3  |  |  |

|   | 1.3   |                                                                       |    |  |  |

|   |       | 1.3.1 Accelerator Integration Tool (AIT)                              | 4  |  |  |

|   |       | 1.3.2 Kernel module                                                   | 5  |  |  |

|   |       | 1.3.3 XDMA                                                            | 5  |  |  |

|   |       | 1.3.4 xTasks                                                          | 5  |  |  |

|   |       | 1.3.5 Nanos6-fpga                                                     | 5  |  |  |

|   |       | 1.3.6 LLVM/Clang                                                      | 6  |  |  |

| 2 | Deve  | elop OmpSs-2@FPGA programs                                            | 7  |  |  |

|   | 2.1   | Limitations                                                           | 7  |  |  |

|   | 2.2   | Specific differences in clauses and directives in Ompss@FPGA VS OmpSs | 7  |  |  |

|   | 2.3   | Clauses of task directive                                             | 8  |  |  |

|   |       | 2.3.1 num_instances                                                   | 8  |  |  |

|   |       | 2.3.2 affinity                                                        | 8  |  |  |

|   |       | 2.3.3 copy_in/out                                                     | 8  |  |  |

|   |       | 2.3.4 copy_deps                                                       | 9  |  |  |

|   | 2.4   | Calls to Nanos6 API                                                   | 9  |  |  |

|   |       | 2.4.1 Nanos6 FPGA Architecture API                                    | 9  |  |  |

| 3 | Com   | pile OmpSs-2@FPGA programs                                            | 11 |  |  |

|   | 3.1   | LLVM/Clang FPGA Phase options                                         | 11 |  |  |

|   |       |                                                                       | 11 |  |  |

|   |       | 3.1.2 fompss-fpga-ait-flags                                           | 11 |  |  |

|   |       | 3.1.3 fompss-fpga-memory-port-width                                   | 12 |  |  |

|   |       | 3.1.4 fompss-fpga-check-limits-memory-port                            | 12 |  |  |

|   | 3.2   | AIT options                                                           | 12 |  |  |

|   |       | 3.2.1 AIT options                                                     | 12 |  |  |

|   |       | 3.2.2 Accelerator placement options                                   | 16 |  |  |

|   |       | 3.2.3 Accelerator interconnect options                                | 19 |  |  |

|   | 3.3   | Binaries                                                              | 22 |  |  |

|   | 3.4   | Bitstream                                                             | 22 |  |  |

|   |       | 3.4.1 Shared memory port                                              | 22 |  |  |

|   | 3.5   | Boot Files                                                            | 22 |  |  |

| 4 | Runi  | ning OmpSs-2@FPGA Programs                                            | 25 |  |  |

|   | 4.1        | Nanose    | 1                                                           | 25 |

|---|------------|-----------|-------------------------------------------------------------|----|

|   |            | 4.1.1     | Nanos6 FPGA Architecture configuration                      | 25 |

| 5 | Crea       | te boot f | files for ultrascale                                        | 27 |

|   | 5.1        |           | aisites                                                     | 27 |

|   |            | 5.1.1     | Petalinux installation                                      | 27 |

|   | 5.2        |           | ux project setup                                            | 27 |

|   | 3.2        | 5.2.1     | Unpack the bsp                                              | 28 |

|   |            | 5.2.2     | [Optional] Fix known problems in AXIOM-ZU9EG-2016.3 project | 28 |

|   |            | 5.2.3     | [Optional] Modify the FSBL to have the Fallback system      | 28 |

|   |            | 5.2.3     |                                                             | 28 |

|   |            |           | Configure petalinux                                         | 28 |

|   | <i>5</i> 2 | 5.2.5     | Configure linux kernel                                      |    |

|   | 5.3        |           | ux (2016.3) build for a custom hdf                          | 29 |

|   |            | 5.3.1     | Add missing nodes to device tree                            | 29 |

|   |            | 5.3.2     | Build the Linux system                                      | 29 |

|   |            | 5.3.3     | [Optional] Build PMU Firmware                               | 30 |

|   |            | 5.3.4     | Create BOOT.BIN file                                        | 30 |

|   | 5.4        | Petalin   | ux (2018.3) build for a custom hdf                          | 30 |

|   |            | 5.4.1     | Add missing nodes to device tree                            | 30 |

|   |            | 5.4.2     | Build the Linux system                                      | 31 |

|   |            | 5.4.3     | Create BOOT.BIN file                                        | 31 |

|   |            |           |                                                             |    |

| 6 | Clust      | ter Insta |                                                             | 33 |

|   | 6.1        | Ikergur   | ne cluster installation                                     | 33 |

|   |            | 6.1.1     | General remarks                                             | 33 |

|   |            | 6.1.2     | Module structure                                            | 33 |

|   |            | 6.1.3     | Build applications                                          | 33 |

|   |            | 6.1.4     | Running applications                                        | 34 |

|   | 6.2        | Xaloc o   | cluster installation                                        | 35 |

|   |            | 6.2.1     | General remarks                                             | 35 |

|   |            | 6.2.2     | Node specifications                                         | 35 |

|   |            | 6.2.3     | Logging into xaloc                                          | 35 |

|   |            | 6.2.4     | Module structure                                            | 36 |

|   |            | 6.2.5     | Build applications                                          | 36 |

|   |            | 6.2.6     |                                                             | 36 |

|   | ( )        |           | Running applications                                        |    |

|   | 6.3        | _         | luster installation                                         | 39 |

|   |            | 6.3.1     | General remarks                                             | 39 |

|   |            | 6.3.2     | Node specifications                                         | 39 |

|   |            | 6.3.3     | Logging into quar                                           | 39 |

|   |            | 6.3.4     | Module structure                                            | 40 |

|   |            | 6.3.5     | Build applications                                          | 40 |

|   |            | 6.3.6     | Running applications                                        | 40 |

|   | 6.4        | crdbma    | ster cluster installation                                   | 44 |

|   |            | 6.4.1     | General remarks                                             | 44 |

|   |            | 6.4.2     | System overview                                             | 44 |

|   |            | 6.4.3     | Logging into the system                                     | 45 |

|   |            | 6.4.4     | Module structure                                            | 45 |

|   |            | 6.4.5     | Build applications                                          | 45 |

|   |            | 6.4.6     | Running applications                                        | 45 |

|   | 6.5        |           | g cluster installation                                      | 48 |

|   | 0.0        | 6.5.1     | General remarks                                             | 48 |

|   |            | 6.5.2     | Logging into llebeig                                        | 48 |

|   |            | 6.5.3     |                                                             | 49 |

|   |            |           | Module structure                                            | -  |

|   |            | 6.5.4     | Build applications                                          | 49 |

| 7   | <b>FAQ:</b> | Frequently Asked Questions                                     | 5  |

|-----|-------------|----------------------------------------------------------------|----|

|     | 7.1         | What is OmpSs-2?                                               | 5  |

|     | 7.2         | How to keep HLS intermediate files generated by Mercurium?     | 5  |

|     | 7.3         | Problems with structure/symbol redefinition in FPGA tasks      | 5  |

|     | 7.4         | Hide/change FPGA task code during Mercurium binary compilation | 5  |

|     | 7.5         | Statically scheduling tasks to different task instances        | 5  |

|     | 7.6         | Remarks/Limitations                                            | 5  |

| Ind | lex         |                                                                | 5' |

The information included in this document is provided "as is", with no warranties whatsoever, including any warranty of merchantability, fitness for any particular purpose, or any warranty otherwise arising out of any proposal, specification, or sample. The document is not guaranteed to be complete and/or error-free at this stage and it is subject to changes without furthernotice. Barcelona Supercomputing Center will not assume any responsibility for errors or omissions in this document. Please send comments, corrections and/or suggestions to ompss-fpga-support at bsc.es. This document is provided for informational purposes only.

**Note:** There is a PDF version of this document at http://pm.bsc.es/ftp/ompss-2-at-fpga/doc/user-guide-3.1.1/ OmpSs2FPGAUserGuide.pdf

CONTENTS 1

2 CONTENTS

# **INSTALL OMPSS-2@FPGA TOOLCHAIN**

This page should help you install the OmpSs-2@FPGA toolchain. However, it is preferable using the pre-build Docker image with the latest stable toolchain. They are available at DockerHUB (https://hub.docker.com/r/bscpm/ompss\_2\_at\_fpga). Moreover, we distribute pre-built SD images for some SoC. Do not hesitate to contact us at <ompss-fpga-support @ bsc.es> if you need help.

First, it describes the prerequisites to do the toolcahin installation. After that, the following sections explain different approaches to do the installation.

# 1.1 Prerequisites

- Git Large File Storage (https://git-lfs.github.com/)

- Python 3.7 or later (https://www.python.org/)

- Vendor backends: Xilinx Vivado 2021.1 or later (https://www.xilinx.com/products/design-tools/vivado.html)

## 1.1.1 Git Large File Storage

AIT repository uses Git Large File Storage to handle relatively-large files that are frequently updated (i.e. hardware runtime IP files) to avoid increasing the history size unnecessarily. You must install it so Git is able to download these files.

Follow instructions on their website to install it.

## 1.1.2 Vendor backends - Xilinx Vivado

Follow the installation instructions from Xilinx Vitis HLS and Vivado. You will need to enable support for the devices you're working on, as well as install the board files for the given devices.

## 1.2 Stable release

There is a meta-repository that points to latest stable version of all tools: https://github.com/bsc-pm-ompss-at-fpga/ompss-2-at-fpga-releases. It contains a Makefile which, based on some environment variables, will compile and install the toolchain. The environment variables are:

- TARGET [Def: aarch64-linux-gnu] Linux architecture that toolchain will target

- PREFIX\_HOST [Def: /] Installation prefix for the host tools (e.g. llvm, ait)

- PREFIX\_TARGET [Def: /] Installation prefix for the target tools (e.g. nanos6, libxdma, libxtasks)

- BUILDCPUS [Def: nproc] Number of processes used for building

The following example will cross-build the toolchain for the *aarch64-linux-gnu* architecture and install it in /opt/bsc/host-arm64/ompss-2 and /opt/bsc/arm64/ompss-2:

```

git clone --recursive https://github.com/bsc-pm-ompss-at-fpga/ompss-2-at-fpga-

→releases.git

cd ompss-2-at-fpga-releases

export TARGET=aarch64-linux-gnu

export PREFIX_HOST=/opt/bsc/host-arm64/ompss-2

export PREFIX_TARGET=/opt/bsc/arm64/ompss-2

make

```

# 1.3 Individual git repositories

The master branches of all tools should generate a compatible toolchain. Each package should contain information about how to compile/install itself, look for the README files. The following points briefly describe each tool and provide a possible build configuration/setup for each one. We assume that all packages will be installed in a Linux OS in the /opt/bsc/arm64/ompss-2 folder. Moreover, we assume that the packages will be cross-compiled from an Intel machine to be run on an ARM64 embedded board.

#### List of tools to install:

- [AIT](https://github.com/bsc-pm-ompss-at-fpga/ait)

- [Kernel module](https://github.com/bsc-pm-ompss-at-fpga/ompss-at-fpga-kernel-module)

- [xdma](https://github.com/bsc-pm-ompss-at-fpga/xdma)

- [xtasks](https://github.com/bsc-pm-ompss-at-fpga/xtasks)

- [Nanos6-fpga](https://github.com/bsc-pm-ompss-at-fpga/nanos6-fpga)

- [LLVM](https://github.com/bsc-pm-ompss-at-fpga/llvm)

# 1.3.1 Accelerator Integration Tool (AIT)

You can install the AIT package through the pip repository python3 -m pip install ait-bsc or cloning the git repository:

```

git clone https://github.com/bsc-pm-ompss-at-fpga/ait

cd ait

git lfs install

git lfs pull

export AIT_HOME="/path/to/install/ait"

export DEB_PYTHON_INSTALL_LAYOUT=deb_system

python3 -m pip install . -t $AIT_HOME

export PATH=PREFIX/ait/:$PATH

export PYTHONPATH=$AIT_HOME:$PYTHONPATH

```

## 1.3.2 Kernel module

The driver is only needed to execute the applications. To compile them, the library must be installed on the host but the kernel module may not be loaded. Example to cross-compile the driver:

```

git clone https://github.com/bsc-pm-ompss-at-fpga/ompss-at-fpga-kernel-module.git cd ompss-at-fpga-kernel-module

export CROSS_COMPILE=aarch64-linux-gnu-

export KDIR=/home/my_user/kernel-headers

export ARCH=arm64

make

```

#### 1.3.3 XDMA

Example to cross-compile the library and install it in the /opt/bsc/arm64/ompss-2/libxdma folder:

```

git clone https://github.com/bsc-pm-ompss-at-fpga/xdma.git cd xdma/src/zynq export CROSS_COMPILE=aarch64-linux-gnu-export KERNEL_MODULE_DIR=/path/to/ompss-at-fpga/kernel/module/src make make PREFIX=/opt/bsc/arm64/ompss-2/libxdma install

```

## 1.3.4 xTasks

Example to cross-compile the library and install it in the /opt/bsc/arm64/ompss-2/libxtasks folder:

```

git clone https://github.com/bsc-pm-ompss-at-fpga/xtasks.git

cd xtasks/src/zynq

export CROSS_COMPILE=aarch64-linux-gnu-

export LIBXDMA_DIR=/opt/bsc/arm64/ompss-2/libxdma

make

make PREFIX=/opt/bsc/arm64/ompss-2/libxtasks install

```

# 1.3.5 Nanos6-fpga

Example to cross-compile the runtime library and install it in the /opt/bsc/arm64/ompss-2/nanos6-fpga folder:

```

git clone https://github.com/bsc-pm-ompss-at-fpga/nanos6-fpga.git

cd nanos6-fpga

./autogen.sh

mkdir build-fpga-arm64

cd build-fpga-arm64

../configure --prefix=/opt/bsc/arm64/ompss-2/nanos6-fpga --host=aarch64-linux-gnu --

--enable-fpga --with-xtasks=/opt/bsc/arm64/ompss-2/libxtasks --disable-discrete-deps --

--disable-all-instrumentations --enable-stats-instrumentation --enable-verbose-

--instrumentation

make

make install

```

# 1.3.6 LLVM/Clang

Example to build a LLVM/Clang cross-compiler that runs on the host and creates binaries for another platform (ARM64 in the example):

```

git clone https://github.com/bsc-pm-ompss-at-fpga/llvm.git

cd llvm

mkdir build-fpga

cd build-fpga

cmake -G Ninja -DCMAKE_INSTALL_PREFIX=/opt/bsc/host-arm64/ompss-2/llvm -DLLVM_TARGETS_

→TO_BUILD="AArch64" -DCMAKE_BUILD_TYPE=Release -DCLANG_DEFAULT_NANOS6_HOME=/opt/bsc/

→arm64/ompss-2/nanos6-fpga -DLLVM_USE_SPLIT_DWARF=ON -DLLVM_ENABLE_PROJECTS="clang" -

→DLLVM_INSTALL_TOOLCHAIN_ONLY=ON -DCMAKE_C_COMPILER=clang -DCMAKE_CXX_

→COMPILER=clang++ -DLLVM_USE_LINKER=lld ../llvm/llvm

nina

ninja install

```

**CHAPTER**

**TWO**

# **DEVELOP OMPSS-2@FPGA PROGRAMS**

Most of the required information to develop an OmpSs-2@FPGA application should be in the general OmpSs-2 documentation (https://pm.bsc.es/ompss-docs/book/index.html). Note that, there may be some unsupported/not-working OmpSs-2 features and/or syntax when using FPGA tasks. If you have some problem or realize any bug, do not hesitate to contact us or open an issue.

To create an FPGA task you need to add the device clause in the task directive. For example:

```

const unsigned int LEN = 8;

#pragma oss task device(fpga) out([LEN]dst, val)

void memset(char * dst, const char val) {

for (unsigned int i=0; i<LEN; ++i) {

dst[i] = val;

}

}</pre>

```

# 2.1 Limitations

There are some limitations when developing an OmpSs@FPGA application:

- Only C/C++ are supported, not Fortran.

- Only function declarations can be annotated as FPGA tasks.

- The HLS source code generated by Clang for each FPGA task will not contain the includes in the original source file but the ones finished in ".fpga.h".

- The FPGA task code cannot perform general system calls, and only some Nanos6 APIs are supported.

- The usage of size\_t, signed long int or unsigned long int is not recommended inside the FPGA accelerator code. They may have different widths in the host and in the FPGA.

# 2.2 Specific differences in clauses and directives in Ompss@FPGA VS OmpSs

Despite OmpSs@FPGA mostly follows the OmpSs behaviour, there are specific clauses or directives that are not yet implemented

- taskyield and atomic directives are not supported.

- critical directive is supported as OmpSs specifies. Specifically: it implements a **global** (all accelerators) mutual exclusion section.

# 2.3 Clauses of task directive

The following sections list the clauses that can be used in the task directive.

# 2.3.1 num\_instances

Defines the number of instances to place in the FPGA bitstream of a task. Usage example:

```

const unsigned int LEN = 8;

#pragma oss task device(fpga) out([LEN]dst) num_instances(3)

void memset(char * dst, const char val) {

for (unsigned int i=0; i<LEN; ++i) {

dst[i] = val;

}

}</pre>

```

# 2.3.2 affinity

The information in this clause is used at runtime to send the tasks to the corresponding FPGA accelerator. This means that a FPGA task has the affinity (0) it will run in accelerator 0 of that type. This clause is useful to manage task scheduling in the user code when there is more than one accelerator of the same type (num\_instances > 1).

```

const unsigned int LEN = 8;

#pragma oss task device(fpga) out([LEN]dst) num_instances(4) affinity(af)

void memset_char(char * dst, const char val, int af) {

for (unsigned int i=0; i<LEN; ++i) {

dst[i] = val;

}

}

#pragma oss task device(fpga) out([size]dst)

void memset_task_creator(float * dst, int size, const float val) {

for (unsigned int i=0; i<size/LEN; ++i) {

memset_char(dst + i*LEN, val, i%4);

}

}</pre>

```

# 2.3.3 copy\_in/out

Defines the memory regions that the FPGA task wrapper must catch in BRAMs/URAMs. This creates a local copy of the parameter in the FPGA task accelerator which can be accessed faster than dispatching memory accesses. The data is copied from the FPGA addressable memory into the FPGA task accelerator before launching the task execution. Depending on the type of clause (copy\_in, copy\_out, copy\_inout), the wrapper includes support for reading/writing the local copy from/into memory. Both input and output data movements, may be dynamically disabled by the runtime based on its knowledge about task copies and predecessor/successor tasks. Usage example:

```

const unsigned int LEN = 8;

#pragma oss task device(fpga) out([LEN]dst) copy_out([LEN]dst)

void memset(char * dst, const char val) {

```

(continues on next page)

```

for (unsigned int i=0; i<LEN; ++i) {

dst[i] = val;

}

</pre>

```

# 2.3.4 copy\_deps

Promote the task dependencies like they were annotated into the copy clause.

# 2.4 Calls to Nanos6 API

The list of Nanos6 APIs and their details can be found in the following section. Note that not all Nanos6 APIs can be called within FPGA tasks and others only are supported within them.

## 2.4.1 Nanos6 FPGA Architecture API

The following sections list and summarize the Nanos++ FPGA Architecture API. The documentation is for the version 10.

#### **Memory Management**

## nanos6\_fpga\_malloc

Allocates memory in the FPGA address space and returns a pointer valid for the FPGA tasks. The returned pointer cannot be dereferenced in the host code.

#### **Arguments:**

- size: Size in bytes to allocate.

- fpga\_addr: Pointer to the FPGA address space as a 64-bit integer.

#### **Return value:**

• NANOS6\_FPGA\_SUCCESS on success, NANOS6\_FPGA\_ERROR on error.

```

typedef enum {

NANOS6_FPGA_SUCCESS,

NANOS6_FPGA_ERROR

} nanos6_fpga_stat_t;

nanos6_fpga_stat_t nanos6_fpga_malloc(uint64_t size, uint64_t* fpga_addr);

```

## nanos\_fpga\_free

```

nanos6_fpga_stat_t nanos6_fpga_free(uint64_t fpga_addr);

```

#### nanos\_fpga\_memcpy

```

typedef enum {

NANOS6_FPGA_DEV_TO_HOST,

NANOS6_FPGA_HOST_TO_DEV

} nanos6_fpga_copy_t;

nanos6_fpga_stat_t nanos6_fpga_memcpy(

void* usr_ptr,

uint64_t fpga_addr,

uint64_t size,

nanos6_fpga_copy_t copy_type);

```

#### **Data copies**

These Nanos6 API only can be called inside an FPGA task. They alloy copies to be performed through a single port that can be wider than the data type being copied.

If any of the data copy API calls are used, the fompss-fpga-memory-port-width option is mandatory.

Data accessed through this functions, has to be aligned to the port width. Otherwise this will result in undefined behaviour.

Also, data should to be **multiple of the port width**. If this cannot be guaranteed, *fompss-fpga-check-limits-memory-port* option is needed so that no out of bounds data is accessed. Otherwise this will result in undefined behaviour.

## nanos6\_fpga\_memcpy\_wideport\_in

```

nanos6_fpga_stat_t nanos6_fpga_memcpy_wideport_in(void* dst, const unsigned long long_

→int addr, const unsigned int num_elems);

```

#### Arguments:

- dst: Pointer to the destination (local) data. It can be any data type.

- addr: FPGA memory address space where the data is stored.

- num\_elems: Number of elements of the array type to be copied.

## nanos6\_fpga\_memcpy\_wideport\_out

```

nanos6_fpga_stat_t nanos6_fpga_memcpy_wideport_out(void* dst, const unsigned long_

→long int addr, const unsigned int num_elems);

```

#### Arguments:

- dst: Pointer to the source (local) data. It can be any data type.

- addr: FPGA memory address space where the data is written.

- num\_elems: Number of elements of the array type to be copied.

**CHAPTER**

THREE

# **COMPILE OMPSS-2@FPGA PROGRAMS**

To compile an OmpSs-2@FPGA program you should follow the general OmpSs-2 compilation procedure using the LLVM/Clang compiler. More information is provided in the OmpSs-2 User Guide (https://pm.bsc.es/ftp/ompss-2/doc/user-guide/llvm/index.html). The following sections detail the specific options of LLVM/Clang to generate the binaries, bitstream and boot files.

The entire list of LLVM/Clang options (for the FPGA phase) and AIT arguments are available here:

# 3.1 LLVM/Clang FPGA Phase options

The following sections list and summarize the LLVM/Clang options from the FPGA Phase.

**Note:** Do not forget the flag -fompss-2 in both compilation and linking stages of your application. Otherwise, your application will not be compiled with parallel support or not linked to the tasking runtime library.

# 3.1.1 fompss-fpga-wrapper-code

```

[Available in release 2.0.0]

```

Enables FPGA task extraction into independent HLS wrappers.

This option is mandatory when generating a bitstream.

```

clang++ -fompss-2 -fompss-fpga-wrapper-code \

src/dotproduct.c -o dotproduct \

-fompss-fpga-ait-flags "--board=alveo_u200 --name=dotproduct"

```

# 3.1.2 fompss-fpga-ait-flags

```

[Available in release 2.0.0]

```

String of whitespace-separated list of AIT flags that will be passed to the tool. Also enables AIT on the linking stage.

This option is mandatory when generating a bitstream.

```

clang++ -fompss-2 \

src/dotproduct.c -o dotproduct \

-fompss-fpga-ait-flags "--board=alveo_u200 --name=dotproduct"

```

# 3.1.3 fompss-fpga-memory-port-width

```

[Available in release 2.0.0]

```

Enables wide-port feature of OmpSs@FPGA.

Accelerator memory interfaces will be merged into a single wide-port of arbitrary power-of-2 size. Code inside the wrapper will be generated in order to pack and unpack local variables when reading and writing from memory.

```

clang++ -fompss-2 -fompss-fpga-memory-port-width 512 \

src/dotproduct.c -o dotproduct \

-fompss-fpga-ait-flags "--board=alveo_u200 --name=dotproduct"

```

# 3.1.4 fompss-fpga-check-limits-memory-port

```

[Available in release 2.0.0]

```

By default the compiler assumes that all the data that has to be copied to and from memory is multiple of the wide-port size.

This option adds checks inside the pack/unpacking code to manage copies smaller than the wide-port size.

```

clang++ -fompss-2 -fompss-fpga-check-limits-memory-port \

src/dotproduct.c -o dotproduct \

-fompss-fpga-ait-flags "--board=alveo_u200 --name=dotproduct"

```

# 3.2 AIT options

# 3.2.1 AIT options

The AIT behavior can be modified with the available options. They are summarized and briefly described in the AIT help, which is:

```

usage: ait -b BOARD -n NAME

The Accelerator Integration Tool (AIT) automatically integrates OmpSs@FPGA_

→accelerators into FPGA designs using different vendor backends.

Required:

-b BOARD, --board BOARD

board model. Supported boards by vendor:

xilinx: alveo_u200, alveo_u250, alveo_u280, alveo_u280_hbm,...

→alveo_u55c, com_express, kv260, simulation, zcu102, zedboard, zybo, zynq702, zynq706

-n NAME, --name NAME project name

Generation flow:

-d DIR, --dir DIR

path where the project directory tree will be created

(def: './')

--disable_IP_caching disable IP caching. Significantly increases generation time

--disable_utilization_check

disable resources utilization check during HLS generation

--disable_board_support_check

disable board support check

--from_step FROM_STEP

initial generation step. Generation steps by vendor:

```

(continues on next page)

```

xilinx: HLS, design, synthesis, implementation, bitstream,

-boot

(def: 'HLS')

--IP_cache_location IP_CACHE_LOCATION

path where the IP cache will be located

(def: '/var/tmp/ait/<vendor>/IP_cache/')

--to_step TO_STEP

final generation step. Generation steps by vendor:

xilinx: HLS, design, synthesis, implementation, bitstream,

→boot

(def: 'bitstream')

Bitstream configuration:

-c CLOCK, --clock CLOCK

FPGA clock frequency in MHz

(def: '100')

--hwcounter

add a hardware counter to the bitstream

--wrapper_version WRAPPER_VERSION

version of accelerator wrapper shell. This information will_

→be placed in the bitstream information

--bitinfo_note BITINFO_NOTE

custom note to add to the bitInfo

Data path:

--datainterfaces_map DATAINTERFACES_MAP

path of mappings file for the data interfaces

--memory_interleaving_stride MEM_INTERLEAVING_STRIDE

size in bytes of the stride of the memory interleaving. By.

→default there is no interleaving

--disable_creator_ports

Disable memory access ports in the task-creation accelerators

Hardware Runtime:

--cmdin_queue_len CMDIN_QUEUE_LEN

maximum length (64-bit words) of the queue for the hwruntime.

→command in

This argument is mutually exclusive with --cmdin_subqueue_len

--cmdin_subqueue_len CMDIN_SUBQUEUE_LEN

length (64-bit words) of each accelerator subqueue for the

→hwruntime command in.

This argument is mutually exclusive with --cmdin_queue_len

Must be power of 2

Def. max(64, 1024/num_accs)

--cmdout_queue_len CMDOUT_QUEUE_LEN

maximum length (64-bit words) of the queue for the hwruntime,

→command out

This argument is mutually exclusive with --cmdout_subqueue_len

--cmdout_subqueue_len CMDOUT_SUBQUEUE_LEN

length (64-bit words) of each accelerator subqueue for the

→hwruntime command out. This argument is mutually exclusive with --cmdout_queue_len

Must be power of 2

Def. max(64, 1024/num_accs)

--disable_spawn_queues

disable the hwruntime spawn in/out queues

--spawnin_queue_len SPAWNIN_QUEUE_LEN

length (64-bit words) of the hwruntime spawn in queue. Must,

\rightarrowbe power of 2

(def: '1024')

```

(continues on next page)

3.2. AIT options

```

--spawnout_queue_len SPAWNOUT_QUEUE_LEN

length (64-bit words) of the hwruntime spawn out queue. Must_

⇒be power of 2

(def: '1024')

--hwruntime_interconnect HWR_INTERCONNECT

type of hardware runtime interconnection with accelerators

centralized

distributed

(def: 'centralized')

--max_args_per_task MAX_ARGS_PER_TASK

maximum number of arguments for any task in the bitstream

(def: '15')

--max_deps_per_task MAX_DEPS_PER_TASK

maximum number of dependencies for any task in the bitstream

(def: '8')

--max_copies_per_task MAX_COPIES_PER_TASK

maximum number of copies for any task in the bitstream

(def: '15')

--enable_pom_axilite enable the POM axilite interface with debug counters

--picos_num_dcts NUM_DCTS

number of DCTs instantiated

(def: '1')

--picos_tm_size PICOS_TM_SIZE

size of the TM memory

(def: '128')

--picos_dm_size PICOS_DM_SIZE

size of the DM memory

(def: '512')

--picos_vm_size PICOS_VM_SIZE

size of the VM memory

(def: '512')

--picos_dm_ds DATA_STRUCT

data structure of the DM memory

BINTREE: Binary search tree (not autobalanced)

LINKEDLIST: Linked list

(def: 'BINTREE')

--picos_dm_hash HASH_FUN

hashing function applied to dependence addresses

P PEARSON: Parallel Pearson function

(def: 'P_PEARSON')

--picos_hash_t_size PICOS_HASH_T_SIZE

DCT hash table size

(def: '64')

User-defined files:

--user_constraints USER_CONSTRAINTS

path of user defined constraints file

--user_pre_design USER_PRE_DESIGN

path of user TCL script to be executed before the design step_

→ (not after the board base design)

--user_post_design USER_POST_DESIGN

path of user TCL script to be executed after the design step

Miscellaneous:

```

(continues on next page)

```

-h, --help

show this help message and exit

-i, --verbose_info print extra information messages

--dump_board_info

dump board info json for the specified board

-j JOBS, --jobs JOBS specify the number of jobs to run simultaneously

By default it will use as many jobs as cores with at least_

→5GB of dedicated free memory, or the value returned by `nproc`, whichever is less.

--mem_per_job MEM_PER_JOB

specify the memory per core used to estimate the number of...

⇒jobs to launch (def: 5G)

-k, --keep_files keep files on error

-v, --verbose

print vendor backend messages

--version

print AIT version and exits

Xilinx-specific arguments:

--floorplanning_constr FLOORPLANNING_CONSTR

built-in floorplanning constraints for accelerators and_

⇒static logic

acc: accelerator kernels are constrained to a SLR region

static: each static logic IP is constrained to its relevant_

→SLR

all: enables both 'acc' and 'static' options

By default no floorplanning constraints are used

--placement_file PLACEMENT_FILE

json file specifying accelerator placement

--slr_slices SLR_SLICES

enable SLR crossing register slices

acc: create register slices for SLR crossing on accelerator-

→related interfaces

static: create register slices for static logic IPs

all: enable both 'acc' and 'static' options

By default they are disabled

--regslice_pipeline_stages REGSLICE_PIPELINE_STAGES

number of register slice pipeline stages per SLR

'x:y:z': add between 1 and 5 stages in master:middle:slave.

→SLRs

auto: let Vivado choose the number of stages

(def: auto)

--interconnect_regslice INTER_REGSLICE_LIST [INTER_REGSLICE_LIST ...]

enable register slices on AXI interconnects

all: enables them on all interconnects

mem: enables them on interconnects in memory datapath

hwruntime: enables them on the AXI-stream interconnects_

⇒between the hwruntime and the accelerators

--interconnect_opt OPT_STRATEGY

AXI interconnect optimization strategy: Minimize 'area' or_

→maximize 'performance'

(def: 'area')

--interconnect_priorities

enable priorities in the memory interconnect

--simplify_interconnection

simplify interconnection between accelerators and memory...

→Might negatively impact timing

--power_monitor

enable power monitoring infrastructure

--thermal monitor

enable thermal monitoring infrastructure

--debug_intfs INTF_TYPE

choose which interfaces mark for debug and instantiate the.

→correspondent ILA cores

```

(continues on next page)

3.2. AIT options

```

AXI: debug accelerator's AXI interfaces

stream: debug accelerator's AXI—Stream interfaces

both: debug both accelerator's AXI and AXI—Stream interfaces

custom: debug user—defined interfaces

none: do not mark for debug any interface

(def: 'none')

--debug_intfs_list DEBUG_INTFS_LIST

path of file with the list of interfaces to debug

--ignore_eng_sample ignore engineering sample status from chip part number

--target_language TARGET_LANG

choose target language to synthesize files to: vhdl or verilog

(def: 'verilog')

environment variables:

PETALINUX_BUILD path where the Petalinux project is located

```

# 3.2.2 Accelerator placement options

This section documents how to constrain accelerators to a particular SLR region in a device.

There are three flags that control accelerator placement:

- Constraints: --floorplanning\_constr

- Slices: --slr\_slices

- Configuration file --placement\_file

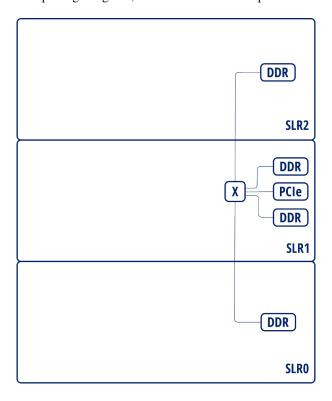

On an Alveo U200, which has 3 Super logic regions, external interfaces are placed as follows:

Fig. 1: Interface layout for Alveo U200

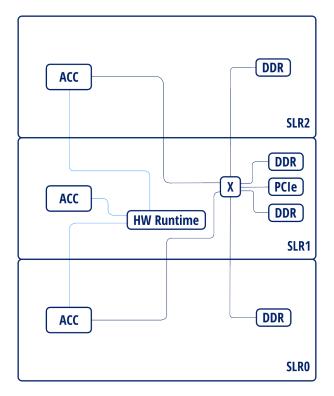

By default, all user accelerators are placed as vivado considers. Sometimes it places a kernel accelerator between 2 SLR, usually negatively impacting timing. Users can enforce accelerators to be constrained to an slr region in order to prevent it from being scattered across multiple SLR. For instance, a user can specify something as follows:

Fig. 2: Placed instance diagram

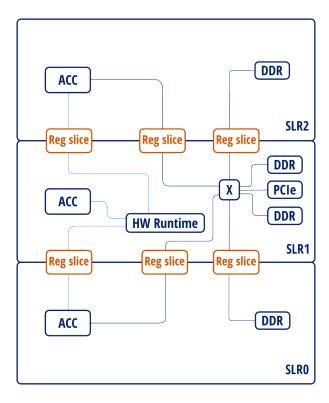

Additionally, users can apply register slices between the SLR crossings to further help timing at the cost of using additional fpga resources. Users can control this by setting different settings for constraints and register slices. For example, activating register slices for the previous design will result in the following layout:

## **User flags**

#### **Constraints**

Constraints affecting different sets of IPs can be individually enabled. This is done by setting the --floorplanning\_constr=<constraint level> flag. This can take four different values: [none], acc, static, all.

These are specified as follows:

#### [none]

Nothing is constrained to a particular region. This is the default behavior.

This is done by not specifying the --floorplanning\_constr

3.2. AIT options

Fig. 3: Placed instance diagram with register slices

#### acc

Accelerator kernels are constrained to be in a slr region.

#### static

Static logic is constrained to a particular region. Each of the static logic IP is constrained to its relevant region. For instance PCI IP is going to be constrained to the slr that contains it IO pins, which is SLR 1 in the case of the U200.

#### all

Enables acc and static

## Slices

Slices can be automatically placed in SLR crossings to improve timing. --slr\_slices flag controls the settings. It can take four different values: [none], acc, static, all.

## [none]

No register slices are created for slr crossing, this is the default behaviour.

This is achieved by omitting --slr\_slices flag.

#### acc

Register slices for SLR crossing are created for accelerator related interfaces: - Accelerator - hw runtime - Accelerator - DDR interconnect

#### static

Register slices are created for static logic (DDR MIGs, PCI, communication infrastructure, etc.).

#### all

Enables both acc and static.

## **Configuration file**

Configuration file is a json file that determines the placement of each accelerator instance. It's specified using the --placement\_file option. It should contain a dictionary of accelerator types.r Each accelerator type must contain a list of SLR numbers, one for each instance, indicating where the accelerator is going to be placed. For instance:

```

"calculate_forces_BLOCK" : [0, 0, 1, 2, 2],

"solve_nbody_task": [1],

"update_particles_BLOCK": [1]

}

```

This constrains 2 of the 4 calculate\_forces\_BLOCK accelerators to be in SLR0, one of them in SLR1 and the remaining 2 in SLR2. Also, solve\_nbody\_task and update\_particles\_BLOCK will be placed in SLR1.

# 3.2.3 Accelerator interconnect options

## Simplified interconnect

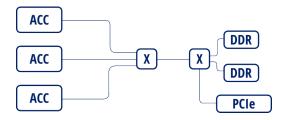

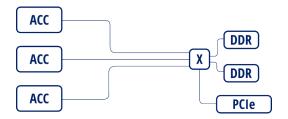

By default, memory interconnection is implemented as 2 interconnection stages:

Fig. 4: 2 stage interconnection

This is done in order to save resources in the case that there's data access ports. However, this serializes data accesses. This prevents accelerators from accessing different memory banks in parallel.

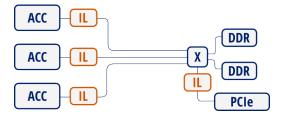

By setting the --simplify\_interconnection will result in the following:

When also setting --interconnect\_opt=performance can allow accelerators to concurrently access different banks, effectively increasing overall available bandwidth. Otherwise, accesses will not be performed in parallel as the interconnect is configured in "area" mode.

3.2. AIT options

Fig. 5: Simplified interconnection

However, the downside is that this can affect timing and resource usage when this interconnection mode is enabled.

#### Memory access interleave

By default, FPGA memory is allocated sequentially. By setting the --memory\_interleaving\_stride=<stride> option will result in allocations being placed in different modules each *stride* bytes. Therefore accelerator memory accesses will be scattered across the different memory interfaces.

For instance, setting --memory\_interleaving\_stride=4096. Will result in the first 4k being allocated to bank 0, next 4k are allocated info bank 1, and so on.

This may improve accelerator memory access bandwidth when combined with *Simplified interconnect* and *Interconnect optimization strategy* options:

Fig. 6: Simplified interconnection with memory interleaving

#### Interconnect optimization strategy

Option --interconnect\_opt=<optimization strategy> defines the optimization strategy for AXI interconnects.

This option only accepts area or performance strategies. While *area* results in lower resource usage, performance is lower than the *performance* setting.

In particular, using *area* prevents access from different slaves into different masters do be performed in parallel. This is specially relevant when using *Simplified interconnect*.

See also Xilinx PG059 for more details on the different strategies.

## Interconnect register slices

By specifying --interconnect\_regslice=<interconnect group> option, it enables *outer and auto* register slice mode on selected interconnect cores.

This mode places an extra *outer* register between the inner interconnect logic (crossbar, width converter, etc.) and the outer core slave interfaces. It also places an *auto* register slice if the slave interface is in the same clock domain. See Xilinx PG059 for details on these modes.

Interconnect groups are defined as follows:

- all: enables them on all interconnects.

- mem: enables them on interconnects in memory data path (accelerator DDR)

- hwruntime: enables them on the AXI-stream interconnects between the hwruntime and the accelerators (accelerator control)

#### Interface debug

Interfaces can be set up for debugging through ILA cores. By setting debugging options, different buses will be set up for debugging and the corresponding ILA cores are generated as needed.

There are two modes to set up debugging, By enabling debug in interface group through --debug\_intf=<interface group> or selecting individual interfaces using --debug\_intf\_list=<interface list files>.

#### Interface group selection

Interfaces can be marked for debug in different groups specified in the --debug\_intf=<interface group>:

- AXI: Debug accelerator's AXI 4 memory mapped data interfaces interfaces

- stream: Debug accelerator's AXI-Stream control interfaces

- both: Debug both AXI and stream interface groups.

- custom: Debug user-defined interfaces

- none: Do not mark for debug any interface (this is the default behaviour)

#### Interface list

Al list of interfaces can be specified in order to enable individual interfaces through the --debug\_intf\_list=<interface list files>option.

Interface list contains a list of interface paths, one for each line. Interface paths are block design connection paths. Ait creates an interface list with all accelerator data interfaces named cproject name>.datainterfaces.txt. First column is the slave end (origin) of the connection and second column specifies the master (destination) end.

Accelerator data interfaces are specified as

```

<accelerator>_<0>/<accelerator>_ompss/<interface name>

```

For instance to debug interface x and y from accelerator foo interface list should look as follows:

```

/foo_0/foo_ompss/m_axi_mcxx_x

/foo_0/foo_ompss/m_axi_mcxx_y

```

3.2. AIT options 21

# 3.3 Binaries

To compile applications with LLVM/Clang you must add the flag -fompss-2 when using either:

- clang++ for C++ applications.

- clang for C applications.

## 3.4 Bitstream

**Note:** LLVM/Clang expects the Accelerator Integration Tool (AIT) to be available on the PATH, if not the linker will fail. Moreover, AIT expects Vitis HLS and Vivado to be available in the PATH.

**Warning:** Sourcing the Vivado settings.sh file may break the cross-compilation toolchain. Instead, just add the directory of vivado binaries in the PATH.

To generate the bitstream, you should enable the bitstream generation in the LLVM/Clang compiler (using the -fompss-fpga-wrapper-code flag) and provide the FPGA linker (aka AIT) flags with -fompss-fpga-ait-flags option. If the FPGA linker flags does not contain the -b (or --board) and -n (or --name) options, the linker phase will fail.

For example, to compile the dotproduct application, in debug mode, for the Alveo U200, with a target frequency of 300Mhz, you can use the following command:

```

clang -fompss-2 -fompss-fpga-wrapper-code \

src/dotproduct.c -o dotproduct-d \

-fompss-fpga-ait-flags "--board=alveo_u200 --clock=300 --name=dotproduct"

```

# 3.4.1 Shared memory port

By default, LLVM/Clang generates an independent port to access the main memory for each task argument. Moreover, the bit-width of those ports equals to the argument data type width. This can result in a huge interconnection network when there are several task accelerators or they have several non-scalar arguments.

This behavior can be modified to generate unique shared port to access the main memory between all task arguments. This is achieved with the <code>-fompss-fpga-memory-port-width</code> option of LLVM/Clang which defines the desired bit-width of the shared port. The value must be a common multiple of the bit-widths for all task arguments.

The usage of the LLVM/Clang variable to generate a 128 bit port in the previous dotproduct command will be like:

```

clang -fompss-2 -fompss-fpga-wrapper-code \

src/dotproduct.c -o dotproduct-d \

-fompss-fpga-memory-port-width 128 \

-fompss-fpga-ait-flags "--board=alveo_u200 --clock=300 --name=dotproduct"

```

# 3.5 Boot Files

Some boards do not support loading the bitstream into the FPGA after the boot, therefore the boot files should be updated and the board rebooted. This step is not needed for the z7000 family of devices as the bitstream can be loaded

after boot. AIT supports the generation of boot files for some boards but the step is disabled by default and should be enabled by hand.

#### First, you need to set the following environment variables:

- PETALINUX\_INSTALL. Petalinux installation directory.

- PETALINUX\_BUILD. Petalinux project directory. See *Create boot files for ultrascale* to have more information about how to setup a petalinux project build.

Then you can invoke AIT with the same options provided in <code>-fompss-fpga-ait-flags</code> and the following new options: <code>--from\_step=boot --to\_step=boot</code>. Also, you may directly add the <code>--to\_step=boot</code> option in <code>-fompss-fpga-ait-flags</code> during the LLVM/Clang launch.

3.5. Boot Files

# **RUNNING OMPSS-2@FPGA PROGRAMS**

To run an OmpSs-2@FPGA program you should follow the general OmpSs-2 run procedure. More information is provided in the OmpSs-2 User Guide (https://pm.bsc.es/ftp/ompss-2/doc/user-guide/nanos6/index.html).

# 4.1 Nanos6 FPGA Architecture options

The Nanos6 behavior can be tuned with different configuration options. They are summarized and briefly described in the Nanos6 default configuration file, the FPGA architecture section is shown below:

# 4.1.1 Nanos6 FPGA Architecture configuration

The Nanos6 behavior can be tuned with different configuration options. They are summarized and briefly described in the Nanos6 default configuration file, the FPGA architecture section is shown below:

```

[devices]

directory = true

[devices.fpga]

# Enable/disable the reverse offload service

reverse_offload = false

# Byte alignment of the fpga memory allocations

alignment = 16

# If xtasks supports async copies, it can be "async", if not, the

→runtime can use the default xtasks memcpy and

# simulate an asynchronous copy spawning a new thread with "forced,

→async". Copies can also be synchronous with "sync".

mem_sync_type = "sync"

page_size = 0x8000

requested\_fpga\_memory = 0x40000000

# Maximum number of FPGA tasks running at the same time

streams = 16

[devices.fpga.polling]

# Indicate whether the FPGA services should constantly run_

\rightarrowwhile there are FPGA tasks

# running on their FPGA. Enabling this option may reduce the

→ latency of processing FPGA

# tasks at the expenses of occupying a CPU from the system._

→ Default is true

pinned = true

# The time period in microseconds between FPGA service runs...

\hookrightarrow During that time, the CPUs

# occupied by the services are available to execute ready_

tasks. Setting this option to 0

```

(continues on next page)

# makes the services to constantly run. Default is 1000

period\_us = 1000

**CHAPTER**

**FIVE**

## CREATE BOOT FILES FOR ULTRASCALE

The newer versions of the Accelerator Integration Tool (AIT) support the automatic generation of boot files for some boards. This includes the steps in *Petalinux* (2016.3) build for a custom hdf or *Petalinux* (2018.3) build for a custom hdf, which are the ones repeated for every BOOT.BIN generation. The steps in *Petalinux project setup* are needed to setup the petalinux project build environment. Assuming that you have a valid petalinux build, you can use the ait functionality with the following points:

- Add the option --to\_step=boot when calling ait.

- Provide the Petalinux installation and project directories using the following environment variables:

- PETALINUX\_INSTALL Petalinux installation directory.

- PETALINUX\_BUILD Petalinux project directory.

The following sections explain how to build a petalinux project and how to generate a BOOT.BIN using this project.

# 5.1 Prerequisites

- Petalinux installer (https://www.xilinx.com/products/design-tools/embedded-software/petalinux-sdk.html).

- Vivado handoff file (hdf) from a synthesized Vivado project.

#### 5.1.1 Petalinux installation

Petalinux is installed running its auto-installer package:

```

./petalinux-v2016.3-final-installer.run

```

After installation, you should source the petalinux environment file. Usually, this needs to be done every time you want to run from a new terminal. Note that the petalinux settings may change the ARM cross compilers breaking the OmpSs@FPGA tool-chain.

source <petalinux install dir>/settings.sh

# 5.2 Petalinux project setup

The following steps should be executed once. After them, you will be able to build different boot files just using the AIT option or executing the steps in any of the following sections: *Petalinux* (2016.3) build for a custom hdf (for Petalinux 2016.3) or *Petalinux* (2018.3) build for a custom hdf (for Petalinux 2018.3).

## 5.2.1 Unpack the bsp

Unpack the bsp to create the petalinux project.

petalinux-create -t project -s <path to petalinux bsp>

# 5.2.2 [Optional] Fix known problems in AXIOM-ZU9EG-2016.3 project

Here are some patches for known problems:

# 5.2.3 [Optional] Modify the FSBL to have the Fallback system

We developed a modification of Xilinx First Stage Boot Loader (FSBL) to support a fallback boot to a valid known BOOT.BIN file. More information in:

# 5.2.4 Configure petalinux

Run petalinux configuration. No changes need to be made to petalinux configuration, but this step has to be run.

```

export GIT_SSL_NO_VERIFY=1 #Ignore broken certificates

petalinux-config

```

After configuration this step, petalinux will download any needed files from external repositories.

# 5.2.5 Configure linux kernel

To enter the kernel configuration utility, run:

petalinux-config -c kernel

#### [Optional] Enable Xilinx DMA driver

**Note:** This step is only needed when the use of DMA engines is desired.

Xilinx driver support has to be enabled in order to support Xilinx DMA engine devices. Usually, this is not needed as OmpSs@FPGA does not make use them to send tasks, neither information, between the host and the FPGA device. It can be enabled in: Device drivers  $\rightarrow$  DMA Engines Support  $\rightarrow$  Xilinx axi DMAS

#### Fix old kernels

## [Optional] Increase the CMA (Contiguous Memory Area)

You may want to increase the CMA size. It is used by Nanos++ as memory for the FPGA device copies. Its size can be set in: Device drivers  $\rightarrow$  Generic Driver Options  $\rightarrow$  DMA Contiguous Memory Allocator

# 5.3 Petalinux (2016.3) build for a custom hdf

Once petalinux project is setup, you can update it to contain a custom bitstream with your hardware. This steps can be repeated several times without executing again the steps in the *Petalinux project setup* section. Moreover, AIT supports the automatic execution of the following steps as explained in the beginning of this page.

First, you need to import the hardware description file (hdf) in the petalinux project. This is done executing the following command in the root directory of the petalinux project build.

```

petalinux-config --get-hw-description <path to application hdf file>

```

# 5.3.1 Add missing nodes to device tree

Some nodes should be added to the device tree before compiling it.

#### misc clk 0

Edit the file ./subsystems/linux/configs/device-tree/pl.dtsi to add or edit the node misc\_clk\_0. It should have the following contents (ensure that clock-frequency is correctly set):

```

misc_clk_0: misc_clk_0 {

compatible = "fixed-clock";

#clock-cells = <0>;

clock-frequency = <200>;

};

```

#### pl bsc.dtsi

AIT will generate a pl\_bsc.dtsi file in the main Vivado project folder. This file contains the missing nodes in the amba\_pl based on your application build. This file must be copied in ./subsystems/linux/configs/device-tree/system-conf.dtsi file.

For example, it will be located in test\_ait/Vivado/test/ folder if the project name is test.

# 5.3.2 Build the Linux system

When the project is correctly updated, you can build it with the following commands:

```

petalinux-build

```

#### Error in fsbl compilation

In some cases, fsbl compilation triggered during the petalinux build can fail. This is due to a bad cleanup from previous compilation. In this cases, a complete fsbl cleanup and a new build must be performed. Note, that this extra cleanup may collision with the steps described in [Optional] Modify the FSBL to have the Fallback system.

```

petalinux-build -c bootloader -x mrproper

petalinux-build

```

# 5.3.3 [Optional] Build PMU Firmware

Run hsi (included in petalinux and Xilinx SDK).

hsi

#### Inside hsi run

```

set hwdsgn [open_hw_design <hardware.hdf>]

generate_app -hw $hwdsgn -os standalone -proc psu_pmu_0 -app zynqmp_pmufw -compile -

→sw pmufw -dir <dir_for_new_app>

```

Warning: As of vivado 2016.3 pmu firmware breaks Trenz's TEBF0808 boot

## 5.3.4 Create BOOT.BIN file

```

petalinux-package --force --boot --fsbl images/linux/zynqmp_fsbl.elf --fpga <path to_

→application bit file> --u-boot images/linux/u-boot.elf

cp BOOT.BIN images/linux/image.ub <path to boot partition>

```

When using PMU firmware, pmu binary has to be included in boot.bin file. To do so, add the --pmufw <pmufw.elf> argument to the petalinux-package command.

# 5.4 Petalinux (2018.3) build for a custom hdf

Once petalinux 2018.3 project is setup, you can update it to contain a custom bitstream with your hardware. This steps can be repeated several times without executing again the steps in the *Petalinux project setup* section. Moreover, AIT supports the automatic execution of the following steps as explained in the beginning of this page.

First, you need to import the hardware description file (hdf) in the petalinux project. This is done executing the following command in the root directory of the petalinux project build.

```

petalinux-config --get-hw-description <path to application hdf file>

```

# 5.4.1 Add missing nodes to device tree

Some nodes should be added to the device tree before compiling it.

### pl\_bsc.dtsi

AIT will generate a pl\_bsc.dtsi file in the main Vivado project folder. This file contains the missing nodes in the amba\_pl based on your application build. For example, it will be located in test\_ait/Vivado/test/ folder if the project name is test. The contents of such file must be placed at the end of ./project-spec/meta-user/recipes-bsp/device-tree/files/system-user.dtsi file. Note that any remaining contents from a previous build must be removed before. The following command will append the pl\_bsc.dtsi content at the end of system-user.dtsi file:

cat <path to vivado project>/pl\_bsc.dtsi >>project-spec/meta-user/recipes-bsp/device-  $\rightarrow$  tree/files/system-user.dtsi

# 5.4.2 Build the Linux system

When the project is correctly updated, you can build it with the following commands:

petalinux-build

### 5.4.3 Create BOOT.BIN file

petalinux-package --force --boot --fsbl images/linux/zynqmp\_fsbl.elf --fpga <path to\_

→application bit file> --u-boot images/linux/u-boot.elf

cp BOOT.BIN images/linux/image.ub <path to boot partition>

**CHAPTER**

SIX

# **CLUSTER INSTALLATIONS**

# 6.1 Ikergune cluster installation

The OmpSs-2@FPGA releases are automatically installed in the Ikergune cluster. They are available through a module file for each target architecture. This document describes how to load and use the modules to compile an example application. Once the modules are loaded, the workflow in the Ikergune cluster should be the same as in the Docker images.

### 6.1.1 General remarks

- All software is installed in a version folder under the /apps/bsc/ARCH/ompss-2/ directory.

- During the updates, the installation will not be available for the users' usage.

- After the installation, an informative email will be sent.

### 6.1.2 Module structure

The ompss-2 modules are:

• ompss-2/x86\_64/\*[release version]\*

This will automatically load the default Vivado version, although an arbitrary version can be loaded before ompss:

```

module load vivado/2023.2 ompss-2/x86_64/git

```

To list all available modules in the system run:

```

module avail

```

Other modules may be required to generate the boot files for some boards, for example:

```

module load petalinux

```

## 6.1.3 Build applications

To generate an application binary and bitstream, you could refer to *Compile OmpSs-2@FPGA programs* as the steps are general enough.

Note that the appropriate modules need to be loaded. See *Module structure*.

# 6.1.4 Running applications

### Log into a worker node (interactive jobs)

Ikergune cluster uses SLURM in order to manage access to computation resources. Therefore, to log into a worker node, an allocation in one of the partitions have to be made.

There are 2 partitions in the cluster: \* ikergune-eth: arm32 zynq7000 (7020) nodes \* ZU102: Xilinx zcu102 board

In order to make an allocation, you must run salloc:

```

salloc -p [partition]

```

#### For instance:

```

salloc -p ikergune-eth

```

Then get the node that has been allocated for you:

```

squeue

```

The output should look similar to this:

| JOBID PARTITION | NAME USER     | ST | TIME  | NODES NODELIST (REASON) |

|-----------------|---------------|----|-------|-------------------------|

| 8547 ikergune-  | bash afilguer | R  | 16:57 | 1 Node-3                |

Then, you can log into your node:

```

ssh ethNode-3

```

# Load ompss kernel module

The ompss-fpga kernel module has to be loaded before any application using fpga accelerators can be run.

Kernel module binaries are provided in

```

/apps/bsc/[arch]/ompss/[release]/kernel-module/ompss_fpga.ko

```

Where arch is one of:

- arm32

- arm64

release is one of the OmpSs@FPGA releases currently installed.

For instance, to load the 32bit kernel module for the git release, run:

```

sudo insmod /apps/bsc/arm32/ompss/git/kernel-module/ompss_fpga.ko

```

You can also run module avail ompss for a list of the currently installed releases.

### **Loading bitstreams**

The fpga bitstream also needs to be loaded before the application can run. The load\_bitstream utility is provided in order to simplify the FPGA configuration.

```

load_bitstream bitstream.bin

```

Note that the .bin file is being loaded. Trying to load the .bit file will result in an error.

### 6.2 Xaloc cluster installation

The OmpSs-2@FPGA releases are automatically installed in the Xaloc cluster. They are available through a module file for each target architecture. This document describes how to load and use the modules to compile an example application. Once the modules are loaded, the workflow in the Xaloc cluster should be the same as in the Docker images.

#### 6.2.1 General remarks

- The OmpSs@FPGA toolchain is installed in a version folder under the /opt/bsc/ directory.

- Third-party libraries required to run some programs are installed in the corresponding folder under the /opt/lib/ directory.

- The rest of the software (Xilinx toolchain, slurm, modules, etc.) is installed under the /tools/ directory.

- During the updates, the installation will not be available for the users' usage.

- Usually, the installation takes about 30 minutes.

- After the installation, an informative email will be sent.

# 6.2.2 Node specifications

- CPU: Dual Intel Xeon X5680

- https://ark.intel.com/content/www/us/en/ark/products/47916/intel-xeon-processor-x5680-12m-cache-3-33-ghz-6-40-gts-in html

- Main memory: 72GB DDR3-1333

- FPGA: Xilinx Versal VCK5000

- https://www.xilinx.com/products/boards-and-kits/alveo/u200.html

## 6.2.3 Logging into xaloc

Xaloc is accessible from HCA ssh.hca.bsc.es Alternatively, it can be accessed through the 4810 port in HCA and ssh connection will be redirected to the actual host:

```

ssh -p 4810 ssh.hca.bsc.es

```

Also, this can be automated by adding a xaloc host into ssh config:

```

Host xaloc

HostName ssh.hca.bsc.es

Port 8410

```

## 6.2.4 Module structure

The ompss-2 modules are:

• ompss-2/x86\_64/\*[release version]\*

This will automatically load the default Vivado version, although an arbitrary version can be loaded before ompss:

```

module load vivado/2023.2 ompss-2/x86_fpga/git

```

To list all available modules in the system run:

```

module avail

```

# 6.2.5 Build applications

To generate an application binary and bitstream, you could refer to *Compile OmpSs-2@FPGA programs* as the steps are general enough.

Note that the appropriate modules need to be loaded. See *Module structure*.

# 6.2.6 Running applications

### Get access to an installed fpga

Xaloc cluster uses SLURM in order to manage access to computation resources. Therefore, to be able to use the resources of an FPGA, an allocation in one of the partitions has to be made.

There is 1 partition in the cluster:

• fpga: a Versal VCK5000 board

The easiest way to allocate an FPGA is to run bash through srun with the --gres option:

```

srun --gres=fpga:BOARD:N --pty bash

```

Where BOARD is the FPGA to allocate, in this case versal, and N the number of FPGAs to allocate, that is 1.

For instance, the command:

```

srun --gres=fpga:versal:1 --pty bash

```

Will allocate the FPGA and run an interactive bash with the required tools and file permissions already set by slurm. To get information about the active slurm jobs, run:

```

squeue

```

The output should look similar to this:

| JOBID PARTITION | NAME USER     | ST | TIME  | NODES | NODELIST (REASON) |

|-----------------|---------------|----|-------|-------|-------------------|

| 1312 fpga       | bash afilguer | R  | 17:14 | 1     | xaloc             |

### **Loading bistreams**

The FPGA bitstream needs to be loaded before the application can run. The <code>load\_bitstream</code> utility is provided in order to simplify the FPGA configuration.

```

load_bitstream.bit [index]

```

The utility receives a second optional parameter to indicate which of the allocated FPGAs to program, the default behavior is to program all the allocated FPGAs with the bitstream.

To know which FPGAs indices have been allocated, run load\_bitstream with the help (-h) option. The output should be similar to this:

```

Usage load_bitstream bitstream.bit [index]

Available devices:

index: jtag pcie usb

0: XXXXXXXXXXXXX 0000:02:00.0 002:002

```

### Set up qdma queues

**Note:** This step is performed by load\_bitstream script, which creates a single bidirectional memory mapped queue. This is only needed if other configuration is needed.

For DMA transfers to be performed between system main memory and the FPGA memory, qdma queues has to be set up by the user *prior to any execution*.

In this case dmactl tool is used. For instance: In order to create and start a memory mapped qdma queue with index 1 run:

```

dmactl qdma02000 q add idx 1 mode mm dir bi

dmactl qdma02000 q start idx 1 mode mm dir bi

```

OmpSs runtime system expects an mm queue at index 1, which can be created with the commands listed above.

In the same fashion, these queues can also be removed:

```

dmactl qdma02000 q stop idx 1 mode mm dir bi

dmactl qdma02000 q del idx 1 mode mm dir bi

```

For more information, see

```

dmactl --help

```

### Get current bitstream info

In order to get information about the bitstream currently loaded into the FPGA, the tool read\_bitinfo is installed in the system.

```

read_bitinfo

```

Note that an active slurm reservation is needed in order to query the FPGA.

This call should return something similar to the sample output for a matrix multiplication application:

```

Reading bitinfo of FPGA 0000:b3:00.0

Bitstream info version: 11

Number of acc: 8

AIT version: 7.1.0

Wrapper version 13

Board base frequency (Hz) 156250000

Interleaving stride 32768

Features:

[ ] Instrumentation

[ ] Hardware counter

[x] Performance interconnect

[ ] Simplified interconnection

[ ] POM AXI-Lite

[x] POM task creation

[x] POM dependencies

[ ] POM lock

[x] POM spawn queues

[ ] Power monitor (CMS) enabled

[ ] Thermal monitor (sysmon) enabled

Cmd In addr 0x2000 len 128

Cmd Out addr 0x4000 len 128

Spawn In addr 0x6000 len 1024

Spawn Out addr 0x8000 len 1024

Managed rstn addr 0xA000

Hardware counter addr 0x0

POM AXI-Lite addr 0x0

Power monitor (CMS) addr 0x0

Thermal monitor (sysmon) addr 0x0

xtasks accelerator config:

type count freq(KHz)

description

5839957875 1 300000 matmulFPGA

7602000973 7 300000

matmulBlock

ait command line:

ait --name=matmul --board=alveo_u200 -c=300 --memory_interleaving_stride=32K --

→simplify_interconnection --interconnect_opt=performance --interconnect_regslice=all_

→--floorplanning_constr=all --slr_slices=all --placement_file=u200_placement_7x256.

→json --wrapper_version 13

Hardware runtime VLNV:

bsc:ompss:picosompssmanager:7.3

bitinfo note:

```

### Remote debugging

Although it is possible to interact with Vivado's Hardware Manager through ssh-based X forwarding, Vivado's GUI might not be very responsive over remote connections. To avoid this limitation, one might connect a local Hardware Manager instance to targets hosted on Quar, completely avoiding X forwarding, as follows.

- 1. On Xaloc, when allocating an FPGA with slurm, a Vivado HW server is automatically launched for each FPGA:

- FPGA 0 uses port 3120

- 2. On the local machine, assuming that Xaloc's HW Server runs on port 3121, let all connections to port 3121 be

forwarded to Xaloc by doing ssh -L 3121:xaloc:3121 [USER]@ssh.hca.bsc.es -p 8410.

- 3. Finally, from the local machine, connect to Xaloc's hardware server:

- Open Vivado's Hardware Manager.

- Launch the "Open target" wizard.

- Establish a connection to the local HW server, which will be just a bridge to the remote instance.

### 6.3 Quar cluster installation

La Quar is a small town and municipality located in the comarca of Berguedà, in Catalonia.

It's also an intel machine containing two Xilinx Alveo U200 accelerator cards.

The OmpSs-2@FPGA releases are automatically installed in the Quar cluster. They are available through a module file for each target architecture. This document describes how to load and use the modules to compile an example application. Once the modules are loaded, the workflow in the Quar cluster should be the same as in the Docker images.

### 6.3.1 General remarks

- The OmpSs@FPGA toolchain is installed in a version folder under the /opt/bsc/directory.

- Third-party libraries required to run some programs are installed in the corresponding folder under the /opt/lib/ directory.

- The rest of the software (Xilinx toolchain, slurm, modules, etc.) is installed under the /tools/ directory.

- During the updates, the installation will not be available for the users' usage.

- Usually, the installation takes about 30 minutes.

- After the installation, an informative email will be sent.

# 6.3.2 Node specifications

- CPU: Intel Xeon Silver 4208 CPU

- https://ark.intel.com/content/www/us/en/ark/products/193390/intel-xeon-silver-4208-processor-11m-cache-2-10-ghz.

html.

- Main memory: 64GB DDR4-3200

- FPGA: Xilinx Alveo U200

- https://www.xilinx.com/products/boards-and-kits/alveo/u200.html

# 6.3.3 Logging into quar

Quar is accessible from HCA ssh.hca.bsc.es Alternatively, it can be accessed through the 4819 port in HCA and ssh connection will be redirected to the actual host:

```

ssh -p 4819 ssh.hca.bsc.es

```

Also, this can be automated by adding a quar host into ssh config:

```

Host quar

HostName ssh.hca.bsc.es

Port 8419

```

#### 6.3.4 Module structure

The ompss-2 modules are:

• ompss-2/x86\_64/\*[release version]\*

This will automatically load the default Vivado version, although an arbitrary version can be loaded before ompss:

```

module load vivado/2023.2 ompss-2/x86_64/git

```

To list all available modules in the system run:

module avail

# 6.3.5 Build applications

To generate an application binary and bitstream, you could refer to *Compile OmpSs-2@FPGA programs* as the steps are general enough.

Note that the appropriate modules need to be loaded. See *Module structure*.

# 6.3.6 Running applications

### Get access to an installed fpga

Quar cluster uses SLURM in order to manage access to computation resources. Therefore, to be able to use the resources of an FPGA, an allocation in one of the partitions has to be made.

There is 1 partition in the cluster:

fpga: two Alveo U200 boards

The easiest way to allocate an FPGA is to run bash through srun with the --gres option:

```

srun --gres=fpga:BOARD:N --pty bash

```

Where BOARD is the FPGA to allocate, in this case alveo\_u200, and N the number of FPGAs to allocate, either 1 or 2.

For instance, the command:

```

srun --gres=fpga:alveo_u200:2 --pty bash

```

Will allocate both FPGAs and run an interactive bash with the required tools and file permissions already set by slurm. To get information about the active slurm jobs, run:

squeue

The output should look similar to this:

| JOBID PARTITION | NAME USER ST    | TIME NODES NODELIST (REASON) |

|-----------------|-----------------|------------------------------|

| 1312 fpga       | bash afilguer R | 17:14 1 quar                 |

## **Loading bistreams**

The FPGA bitstream needs to be loaded before the application can run. The <code>load\_bitstream</code> utility is provided in order to simplify the FPGA configuration.

```

load_bitstream bitstream.bit [index]

```

The utility receives a second optional parameter to indicate which of the allocated FPGAs to program, the default behavior is to program all the allocated FPGAs with the bitstream.

To know which FPGAs indices have been allocated, run load\_bitstream with the help (-h) option. The output should be similar to this:

```

Usage load_bitstream bitstream.bit [index]

Available devices:

index: jtag pcie usb

0: 21290594G00LA 0000:b3:00.0 001:002

1: 21290594G00EA 0000:65:00.0 001:003

```

### Set up qdma queues

**Note:** This step is performed by load\_bitstream script, which creates a single bidirectional memory mapped queue. This is only needed if other configuration is needed.

For DMA transfers to be performed between system main memory and the FPGA memory, qdma queues has to be set up by the user *prior to any execution*.

In this case dmactl tool is used. For instance: In order to create and start a memory mapped qdma queue with index 1 run:

```

dmactl qdmab3000 q add idx 1 mode mm dir bi

dmactl qdmab3000 q start idx 1 mode mm dir bi

```

OmpSs runtime system expects an mm queue at index 1, which can be created with the commands listed above.

In the same fashion, these queues can also be removed:

```

dmactl qdmab3000 q stop idx 1 mode mm dir bi

dmactl qdmab3000 q del idx 1 mode mm dir bi

```

For more information, see

```

dmactl --help

```

### Get current bitstream info

In order to get information about the bitstream currently loaded into the FPGA, the tool read\_bitinfo is installed in the system.

```

read_bitinfo

```

Note that an active slurm reservation is needed in order to query the FPGA.

This call should return something similar to the sample output for a matrix multiplication application:

```

Reading bitinfo of FPGA 0000:b3:00.0

Bitstream info version: 11

Number of acc: 8

AIT version: 7.1.0

Wrapper version 13

Board base frequency (Hz) 156250000

Interleaving stride 32768

Features:

[ ] Instrumentation

[ ] Hardware counter

[x] Performance interconnect

[ ] Simplified interconnection

[ ] POM AXI-Lite

[x] POM task creation

[x] POM dependencies

[ ] POM lock

[x] POM spawn queues

[ ] Power monitor (CMS) enabled

[ ] Thermal monitor (sysmon) enabled

Cmd In addr 0x2000 len 128

Cmd Out addr 0x4000 len 128

Spawn In addr 0x6000 len 1024

Spawn Out addr 0x8000 len 1024

Managed rstn addr 0xA000

Hardware counter addr 0x0

POM AXI-Lite addr 0x0

Power monitor (CMS) addr 0x0

Thermal monitor (sysmon) addr 0x0

xtasks accelerator config:

count freq(KHz) description

5839957875 1 300000 matmulFPGA

7602000973 7 300000

matmulBlock

ait command line:

ait --name=matmul --board=alveo_u200 -c=300 --memory_interleaving_stride=32K --

→simplify_interconnection --interconnect_opt=performance --interconnect_regslice=all...

→json --wrapper_version 13

Hardware runtime VLNV:

bsc:ompss:picosompssmanager:7.3

bitinfo note:

```

### Remote debugging