OmpSs-at-FPGA is an extension of OmpSs-2 programming model to support easily offloading tasks to FPGA devices. It uses the task and target directives to define the portions of application code that will become accelerators in the FPGA. The supported languages are C and C++.

Source Code Example

The following code shows an implementation of the dot product using an FPGA task.

const int BSIZE = 64;

#pragma oss task device(fpga) in([BSIZE]v1, [BSIZE]v2) inout([1]result)

void dotProduct(float *v1, const float *v2, float *result) {

int resultLocal = result[0];

for (int i = 0; i < BSIZE; ++i) {

resultLocal += v1[i]*v2[i];

}

result[0] = resultLocal;

}

int main() {

unsigned int vecSize = 256;

float v1[vecSize];

float v2[vecSize];

// Initialize the vectors

// ...

float result = 0;

for (int i = 0; i < vecSize; i += BSIZE) {

dotProduct(v1+i, v2+i, &result);

}

#pragma oss taskwait

// Somehow use the result value

// ...

}

Compilation

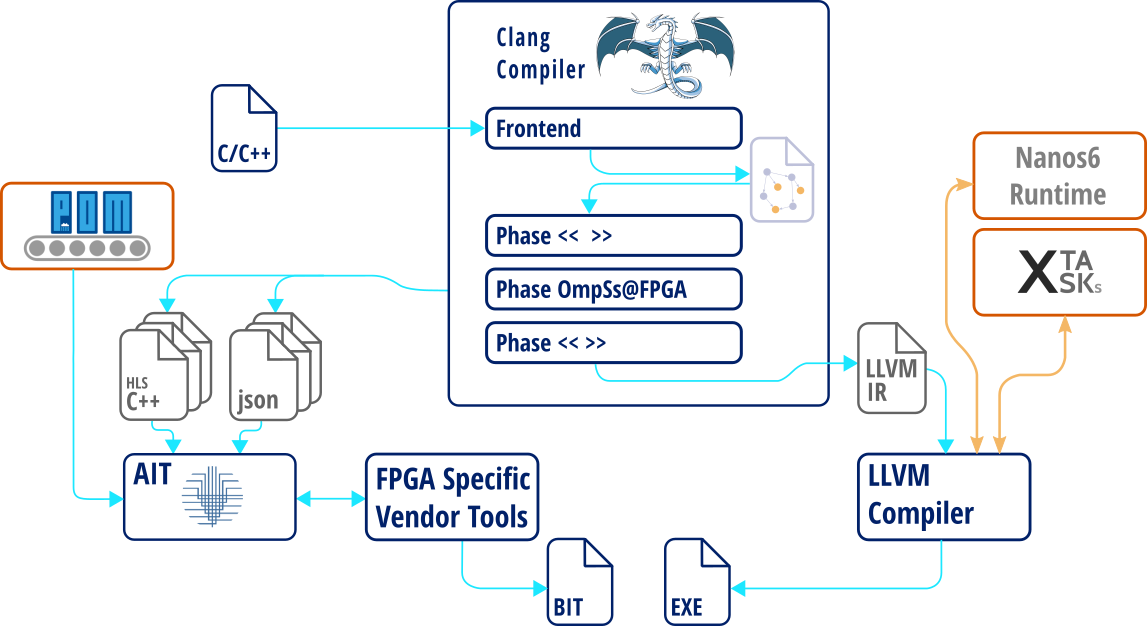

The tasks with fpga target device are isolated by the LLVM/Clang compiler into separate files. These files are used by AIT tool to generate the FPGA bitstream. AIT interfaces with the FPGA vendor tools to generate a bitstream with a generic interface that allows the OmpSs-2 runtime (Nanos6) interact with the FPGA task accelerators. The structure of the components involved in the application binary and FPGA bitstream generation are shown in the below figure.

Execution

The execution of an OmpSs-2@FPGA application follows the same pattern of a regular OmpSs-2 application. The Nanos6 Runtime Library, along with some extra support libraries (xTasks, xdma, etc.), must be available in the execution machine. Then, running the application is as simple as running any other binary.

Supported Boards

Currently, we have tested the toolchain and successfully accelerated different OmpSs-2 applications in the following boards:

- Alveo Family

- U200

- U250

- U280

- U55C

- Zynq Ultrascale+ Family

- Zynq U+ ZCU102

- Kria KV260

- Zynq 7000 Family

- Zedboard

- Zynq 702

- Zynq 706

- Digilent Zybo Zynq 7000

Contact

If you are interested in OmpSs-2@FPGA and want more information, do not hesitate to contact us or send an e-mail: ompss-fpga-support [at] bsc.es

Toolchain Source code

The toolchain source code is available at Github.